Современные системы цифровой обработки сигналов широко используют высокопроизводительные процессоры цифровой обработки сигналов (ВПЦОС). Аппаратура на их основе используется при обработке радиолокационной информации, изображений в реальном времени, цифровой обработке речевых сигналов, в системах радиосвязи, системах дистанционного зондирования атмосферы, цифровой измерительной аппаратуре, находит широкое применение в системах управления транспортными, авиационно-космическими и энергетическими комплексами.

В данной работе рассматривается реализация на высокопроизводительном процессоре цифровой обработки сигналов (ВПЦОС), разработанном ЗАО «ПКК Миландр» [2], алгоритма согласованной фильтрации ЛЧМ сигнала [3]. Производится сравнение полученных результатов с результатами реализации алгоритма на процессоре ADSP-TS201 TigerSHARC фирмы Analog Devices [4,5].

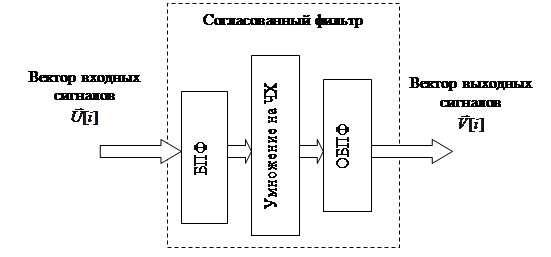

Одним из способов реализации согласованного фильтра (СФ) является фильтрация в частотной области. Для этого входные данные подвергается прямому преобразованию Фурье (БПФ), затем производится умножение полученного спектра на комплексно сопряженный спектр ЛЧМ сигнала в частотной области, и последним этапом является обратное преобразование Фурье (ОБПФ), результата перемножения спектров (рисунок 1).

Перед первым преобразованием длина каждого входного массива дополняется нулями до значения не меньшего длительности линейной свертки входного сигнала и импульсной характеристики согласованного фильтра и кратного степени 2.

Рис.1. Структурная схема СФ

Функция, реализующая алгоритм согласованной фильтрации (рисунок 1), была реализована в виде отдельного модуля на языке ассемблера. Блок-схема алгоритма фильтрации представлена на рисунке 2.

Рис.2. Блок-схема алгоритма согласованной фильтрации

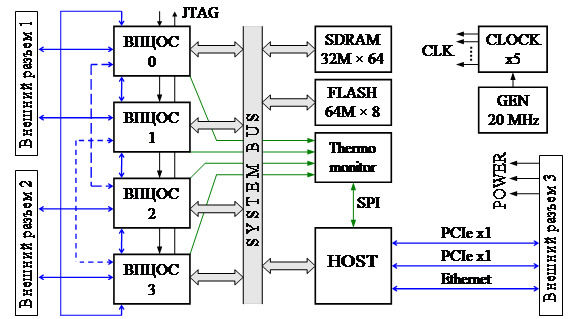

Для реализации алгоритма использовался многопроцессорный (интегрированный) модуль (ИМ) на ВПЦОС ЗАО «ПКК Миландр», разработанный на кафедре информационных радиосистем Нижегородского государственного технического университета им. Р.Е. Алексеева [1]. Структура ИМ показана на рисунке 3.

Рис. 3. Структура ИМ

В состав модуля входят:

- четыре процессора обработки сигналов ВПЦОС0 – ВПЦОС3;

- блок синхронной динамической памяти SDRAM объемом 256МБайт;

- постоянное запоминающее устройство FLASH объемом 64МБайта;

- контроллер системной шины (HOST), выполненный на базе микросхемы FPGA Virtex-6 фирмы Xilinx XC6VLX130T;

- температурный монитор Thermo monitor на базе двух микросхем TMP422 (или TMP423) фирмы Texas Instruments;

- опорный генератор синхронизации GEN с частотой 20МГц;

- умножитель на 5 частоты опорного генератора CLOCKx5.

Процессоры ВПЦОС, динамическая память, постоянная память и контроллер подключены к системной шине кластера SYSTEM BUS разрядностью данных 64 бита. Два LINK-порта каждого процессора используются для организации кольцевой связи (сплошные линии на рисунке 1) и по одному – для организации возможных перекрестных связей (штриховые линии на рисунке 1). По одному LINK-порту каждого процессора выводится на внешние разъемы. HOST-контроллер обеспечивает доступ к системной шине процессорного кластера через внешние интерфейсы Ethernet и PCI-Express.

Сигнальный процессор ВПЦОС ЗАО «ПКК Миландр, использованный в ИМ имеет следующие характеристики:

· Тактовая частота ядра – до 500 МГц;

· Объем встроенной статической памяти – 24 Мбит;

· Пиковая производительность – 3000 MFLOP;

· Разрядность внешней шины – 64 бит;

· Пропускная способность внутренней памяти – 25,2 ГБайт/с;

· Пропускная способность внешней шины – 800 МБайт/с;

· Количество внешних последовательных портов – 4;

· Пропускная способность внешнего последовательного порта – 1 ГБайт/с;

· Полное соответствие при выполнении инструкций аналогу – процессору фирмы Analog Devices ADSP-TS201S TigerSHARC (2 АЛУ с плавающей точкой);

· 14 канальный контроллер прямого доступа к памяти;

· Встроенный арбитр мультипроцессорной шины, исключающий конфликты шины.

При реализации алгоритма использовались следующие возможности процессоров:

· встроенные счетчики циклов;

· чтение и запись квадрословами;

· постинкрементация, арифметические и логические операции с указателями;

· встроенная адресация циклических буферов;

· условные отложенные переходы с предсказанием и без предсказания ветвления;

· безусловные отложенные переходы;

· исполнение нескольких команд за один такт;

· пересылка регистров через АЛУ.

В таблице 1 приведены результаты выполнения алгоритма согласованной фильтрации (рисунок 2) на процессоре ВПЦОС «ПКК Миландр».

Таблица 1

Данные временных затрат СФ

|

Размер БПФ |

Машинных тактов процессора на 1 отсчет комплексных входных данных |

|

|

|

ВПЦОС ЗАО «ПКК Миландр» |

TigerSHARC ADSP-TS201 |

|

256 |

31 |

47 |

|

512 |

33 |

47 |

|

1024 |

35 |

60 |

|

2048 |

37 |

74 |

|

4096 |

39 |

80 |

Для сравнения в таблице приведены данные, полученные с использованием процессора TigerSHARC ADSP-TS201 фирмы Analog Devices.

Анализируя результаты, представленные в таблице 1, можно сделать вывод о том, что при реализации указанного алгоритма скорость вычислений ВПЦОС ЗАО «ПКК Миландр» превосходит скорость вычислений процессора TigerSHARC ADSP-TS201S.

Сравнительный анализ результатов реализации алгоритма согласованной фильтрации ЛЧМ сигнала в частотной области на процессоре TigerSHARC ADSP-TS201 фирмы Analog Devices и ВПЦОС Российской компании ЗАО «ПКК Миландр» показал, что при реализации данного алгоритма время, затрачиваемое ВПЦОС на вычисления значительно меньше времени, затрачиваемого процессором TigerSHARC ADSP-TS201S. Это позволяет утверждать, что разработанный отечественный сигнальный процессор не уступает по характеристикам сигнальному процессору TigerSHARC ADSP-TS201S и позволяет обеспечить решение практически важных задач цифровой обработки сигналов, в частности, задач радиолокационного обнаружения.

Работа выполнена при поддержке Министерства образования и науки РФ в рамках договора № 02.G25.31.0061 от «12» февраля 2013 года (в соответствии с Постановлением Правительства Российской Федерации от 9 апреля 2010 г. № 218).

Рецензенты:

Хранилов В.П., д.т.н., профессор кафедры компьютерных технологий в проектировании и производстве Нижегородского государственного технического университета имени Р.Е. Алексеева, г. Нижний Новгород;

Есипенко В.И., д.ф.-м.н., профессор кафедры «Электроника и сети ЭВМ» Нижегородского государственного технического университета имени Р.Е. Алексеева, г. Нижний Новгород.

Библиографическая ссылка

Огурцов А.Г., Кузин А.А., Кочубейник И.В. РЕАЛИЗАЦИЯ АЛГОРИТМА СОГЛАСОВАННОЙ ФИЛЬТРАЦИИ НА ВЫСОКОПРОИЗВОДИТЕЛЬНОМ ПРОЦЕССОРЕ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ // Современные проблемы науки и образования. 2015. № 2-2. ;URL: https://science-education.ru/ru/article/view?id=22639 (дата обращения: 18.04.2026).