Scientific journal

Modern problems of science and education

ISSN 2070-7428

"Перечень" ВАК

ИФ РИНЦ = 0,936

THE IMPLEMENTATION OF VECTOR LIMITATION OF COMPLEX SIGNAL MAGNITUDE FOR THE HIGH-PERFORMANCE DIGITAL SIGNAL PROCESSOR

Современные системы цифровой обработки сигналов широко используют высокопроизводительные процессоры цифровой обработки сигналов (ВПЦОС). Аппаратура на их основе используется при обработке радиолокационной информации, изображений в реальном времени, цифровой обработке речевых сигналов, в системах радиосвязи, системах дистанционного зондирования атмосферы, цифровой измерительной аппаратуре, находит широкое применение в системах управления транспортными, авиационно-космическими и энергетическими комплексами.

В данной работе рассматривается реализация на высокопроизводительном процессоре цифровой обработки сигналов (ВПЦОС), разработанном ЗАО «ПКК Миландр» [2], алгоритма векторного ограничения комплексного сигнала (ВОГР) [3], широко используемого в системах цифровой обработки сигналов для защиты от преднамеренных и непреднамеренных импульсных помех. Производится сравнение полученных результатов с результатами реализации алгоритма на процессоре ADSP-TS201 TigerSHARC фирмы AnalogDevices [4,5].

Алгоритм ВОГР может быть использован для ограничения амплитуды комплексных отсчетов импульсных помех в сигналах РЛС. При этом для каждого комплексного отсчета входного сигнала выполняется проверка условия: если квадрат амплитуды отсчета больше квадрата заданного порогового уровня, то квадратуры входного отсчета заменяются значениями, вычисленными по следующей формуле

xiОГР = (xi*Uпор)/(xi2+yi2)1/2,

yiОГР = (yi*Uпор)/(xi2+yi2)1/2,

где xiОГРиyiОГР – квадратуры комплексного отсчета после ограничения,xiиyi– квадратуры комплексного отсчета до ограничения, Uпор – пороговое значение.

Если условие превышения квадрата порога не выполняется, то такой отсчет остается без изменения.

Расчет порога ограничения производится по следующей формуле: Uпорi = g·σi, где σi2 - оценка мощности сигнала приi-м положении скользящего окна, i - номер элемента разрешения по дальности, g- коэффициент порогового устройства.

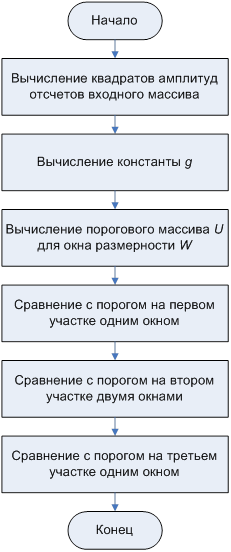

Функция, реализующая алгоритм ВОГР, реализована в виде отдельного модуля на языке ассемблера. Для оптимизации скорости выполнения программы алгоритм разбит на 6 блоков. Первый блок, выполняющий вычисление квадратов амплитуд входного массива отсчетов, реализуется путем вызова оптимизированной функции перемножения двух массивов комплексных чисел с одновременным комплексным сопряжением одного из входных массивов. Во втором блоке вычисляется константа, используемая для вычисления оценки мощности сигнала в скользящем окне. Точность вычисления до последнего значащего бита, формат с плавающей точкой одинарной точности. Далее, в третьем блоке вычисляется служебный массив U, элементы которого представляют собой оценку мощности сигнала внутри скользящего окна, при этом сдвиг окна соответствует порядковому номеру элемента в массиве U. На следующих трех этапах алгоритма производится сравнение значения квадрата амплитуды входных отсчетов и значений порога из массива U. Вся дистанция разбивается на три участка, при этом на первом участке для оценки мощности используется одно окно, расположенное позже анализируемого отсчета, на втором участке используется два окна, располагающиеся ранее и позднее анализируемого отсчета через интервал M точек, и на третьем участке используется одно окно, расположенное ранее анализируемого отсчета.

Дополнительно в программе используется 2 массива для промежуточных вычислений длиной 2·D и D слов.

На рисунке 1 изображена блок-схема программы, реализующей алгоритм ВОГР.

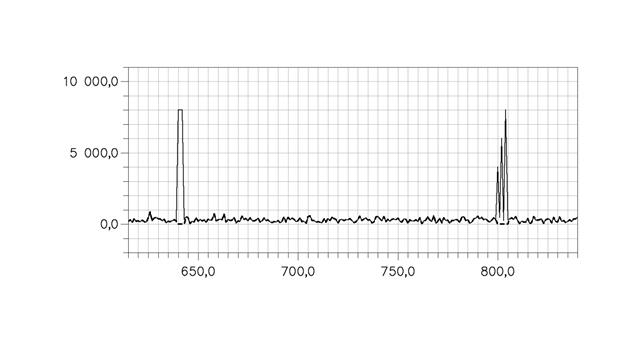

Результаты работы программы приведены на рисунке 2. На рисунке показаны входной (сплошная линия) и выходной (пунктирная линия) сигналы функции ВОГР, при длине окна W=16 и интервале M=4.

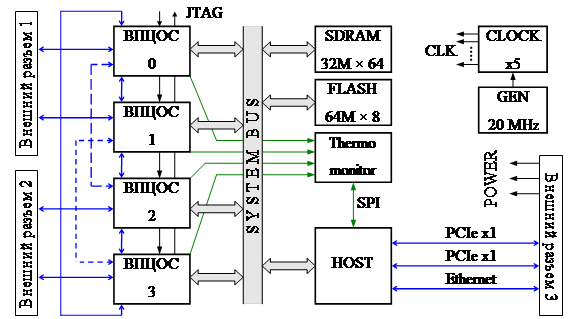

Для реализации алгоритма использовался многопроцессорный (интегрированный) модуль (ИМ) на ВПЦОС ЗАО «ПКК Миландр», разработанный на кафедре информационных радиосистем Нижегородского государственного технического университета им. Р.Е. Алексеева [1]. Структура ИМ показана на рисунке 3.

В состав модуля входят:

- четыре процессора обработки сигналов ВПЦОС0 – ВПЦОС3;

- блок синхронной динамической памяти SDRAM объемом 256МБайт;

- постоянное запоминающее устройство FLASH объемом 64МБайта;

- контроллер системной шины (HOST), выполненный на базе микросхемы FPGA Virtex-6 фирмы XilinxXC6VLX130T;

- температурный монитор Thermomonitor на базе двух микросхем TMP422 (или TMP423) фирмы TexasInstruments;

- опорный генератор синхронизации GEN с частотой 20МГц;

- умножитель на 5 частоты опорного генератора CLOCKx5.

Рис.1. Алгоритм работы программы ВОГР

Рис.2.Входной и выходной сигнал ВОГР

Процессоры ВПЦОС, динамическая память, постоянная память и контроллер подключены к системной шине кластера SYSTEM BUS разрядностью данных 64 бита. Два LINK-порта каждого процессора используются для организации кольцевой связи (сплошные линии на рисунке 1) и по одному – для организации возможных перекрестных связей (штриховые линии на рисунке 1). По одному LINK-порту каждого процессора выводится на внешние разъемы. HOST-контроллер обеспечивает доступ к системной шине процессорного кластера через внешние интерфейсы Ethernet и PCI-Express.

Рис.3. Структура ИМ

При реализации алгоритма использовались следующие возможности процессоров:

- встроенные счетчики циклов;

- чтение и запись квадрословами;

- постинкрементация, арифметические и логические операции с указателями;

- встроенная адресация циклических буферов;

- условные отложенные переходы с предсказанием и без предсказания ветвления;

- безусловные отложенные переходы;

- исполнение нескольких команд за один такт;

- пересылка регистров через АЛУ.

В таблице 1 приведены результаты выполнения алгоритма векторного ограничения на процессоре ВПЦОС «ПКК Миландр».

Таблица 1

Данные временных затрат функции ВОГР

|

Длина окна |

Машинных тактов процессора на 1 отсчет комплексных входных данных |

|

|

|

ВПЦОС ЗАО «ПКК Миландр» |

TigerSHARCADSP-TS201 |

|

256 |

20 |

19 |

|

512 |

21 |

25 |

|

1024 |

31 |

31 |

|

2048 |

30 |

34 |

|

4096 |

33 |

39 |

Для сравнения в таблице приведены данные, полученные с использованием процессора TigerSHARCADSP-TS201 фирмы AnalogDevices.

Сравнительный анализ результатов реализации алгоритма векторного ограничения комплексных сигналов на процессоре TigerSHARCADSP-TS201 фирмы AnalogDevices и ВПЦОС российской компании АО «ПКК Миландр» показал, что при реализации данного алгоритма скорость вычислений ВПЦОС АО «ПКК Миландр» практически совпадает со скоростью вычислений процессора TigerSHARCADSP-TS201S.

Это позволяет утверждать, что разработанный отечественный сигнальный процессор не уступает по характеристикам сигнальному процессору TigerSHARCADSP-TS201S и позволяет обеспечить решение практически важных задач цифровой обработки сигналов, в частности, задач радиолокационного обнаружения.

Работа выполнена при поддержке Министерства образования и науки РФ в рамках договора № 02.G25.31.0061 от «12» февраля 2013 года (в соответствии с Постановлением Правительства Российской Федерации от 9 апреля 2010 г. №218)

Рецензенты:

Хранилов В.П., д.т.н., профессор кафедры компьютерных технологий в проектировании и производстве Нижегородского государственного технического университета имени Р.Е.Алексеева, г. Нижний Новгород;

Утробин В.А., д.т.н., профессор кафедры вычислительных систем и технологий Нижегородского государственного технического университета имени Р.Е.Алексеева, г. Нижний Новгород.

Библиографическая ссылка

Огурцов А.Г., Кузин А.А., Кочубейник И.В. РЕАЛИЗАЦИЯ АЛГОРИТМА ВЕКТОРНОГО ОГРАНИЧЕНИЯ АМПЛИТУДЫ КОМПЛЕКСНОГО СИГНАЛА НА ВЫСОКОПРОИЗВОДИТЕЛЬНОМ ПРОЦЕССОРЕ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ // Современные проблемы науки и образования. 2015. № 2-2. ;URL: https://science-education.ru/en/article/view?id=23162 (дата обращения: 17.05.2026).